分段DAC

當我們需要設(shè)計一個具有特定性能的DAC時,很可能沒有任何一種架構(gòu)是理想的。這種情況下,可以將兩個或更多DAC組合成一個更高分辨率的DAC,以獲得所需的性能。這些DAC可以是同一類型,也可以是不同類型,各DAC的分辨率無需相同。

原則上,一個DAC處理MSB,另一個DAC處理LSB,其輸出以某種方式相加。這一過程稱為“分段”,這些更復(fù)雜的結(jié)構(gòu)稱為“分段DAC”。有許多不同類型的分段DAC,本指南不可能逐一說明,但會介紹其中的幾種。

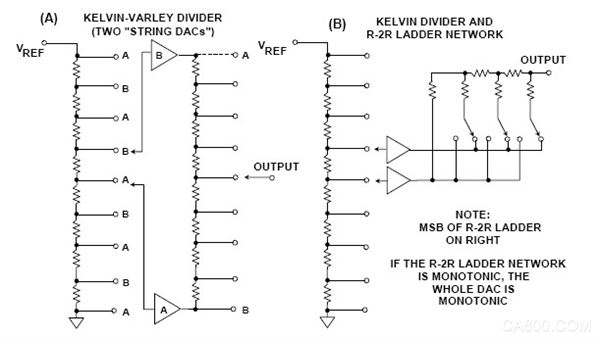

圖1顯示了兩類分段電壓輸出DAC。圖1A中的架構(gòu)有時稱為Kelvin-Varley分壓器,由兩個或更多“串DAC”組成。第一級與第二級之間存在緩沖器,因此第二個串DAC不會加載第一個串DAC,該串中的電阻值無需與另一個串中的電阻值相同。然而,各串中的所有電阻必須彼此相等,否則DAC將不是線性的。示例的第一級和第二級均為3位,但為了具有普遍意義,我們稱第一(MSB)級的分辨率為M位,第二(LSB)級的分辨率為K位,總分辨率為N=M+K位。MSB DAC具有2M個等值電阻,LSB DAC具有2K個等值電阻。

圖1:分段式電壓-輸出DAC

當然,緩沖放大器具有失調(diào),這可能會在緩沖分段串DAC中造成非單調(diào)性。在緩沖Kelvin-Varley分壓器緩沖器的更簡單配置中(圖1A),緩沖器A總是“低于”(電位低于)緩沖器B,LSB串DAC上標“A”的額外抽頭是不必要的。數(shù)據(jù)解碼電路僅為兩個優(yōu)先級編碼器。然而,在此配置中,緩沖器失調(diào)可能會造成非單調(diào)性。

但是,如果將MSB串DAC的解碼電路做得更復(fù)雜一點,使得緩沖器A只能連接到MSB串DAC標“A”的抽頭,緩沖器B只能連接到標“B”的抽頭,則緩沖器失調(diào)將無法造成非單調(diào)性。當然,LSB串DAC解碼必須改變方向,緩沖器需要跳躍連接到另一端,LSB串DAC的抽頭A和B不需要交替,但這需要略微復(fù)雜一點的邏輯,而性能的提高證明這樣做是值得的。

也可以不使用第二個電阻串,而是使用一個二進制DAC來產(chǎn)生三個LSB,如圖1B所示。制造極高分辨率的R-2R梯形電阻網(wǎng)絡(luò)非常困難,更確切地說,很難將其調(diào)整為單調(diào)性。因此,常見的情況是LSB使用由梯形電阻網(wǎng)絡(luò),2到5個MSB則使用其它結(jié)構(gòu)來合成高分辨率DAC。圖1B所示的電壓輸出DAC由一個3位串DAC和一個3位緩沖電壓模式梯形電阻網(wǎng)絡(luò)組成。

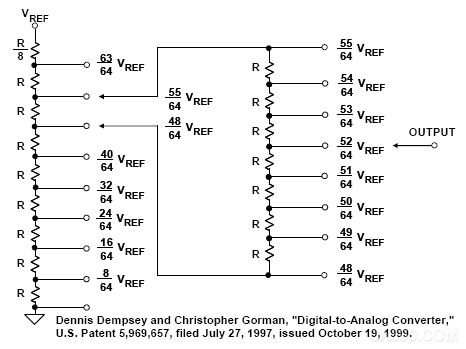

圖2:分段無緩沖串DAC使用專利架構(gòu)

無緩沖的分段串DAC架構(gòu)如圖2所示。在原理上,這種形式更巧妙,并且可以通過CMOS工藝制造(它能制造電阻和開關(guān),但不能制造放大器),因此也更便宜。這種架構(gòu)本身即具備單調(diào)性。

本例中,兩個串中的電阻必須等值,唯一的例外是MSB串中的頂端電阻必須較小(其它電阻值的1/2K),此外LSB串具有2K–1個電阻,而不是2K個。由于沒有緩沖器,LSB串看起來像是與它切換并加載的MSB串中的電阻并聯(lián),這就使得該MSB電阻上的電壓降低LSB串DAC的1 LSB,而這正是所需要的結(jié)果。由于無緩沖,此DAC的輸出阻抗隨著數(shù)字代碼的改變而變化。

為了更好地了解這一巧妙的原理,對于圖2所示的由兩個3位串DAC組成的6位分段DAC,我們計算并標示出了各抽頭的實際電壓。建議讀者將第二個串DAC連接到第一個串DAC中的任何其它電阻兩端,完成這一簡單的分析過程并驗證結(jié)果。關(guān)于無緩沖分段串DAC的詳細數(shù)學(xué)分析,請參閱ADI公司的Dennis Dempsey和Christopher Gorman于1997年申請的相關(guān)專利(參考文獻1)。

適合視頻、通信和其它高頻重構(gòu)應(yīng)用的極高速DAC常常采用完全解碼電流源陣列來構(gòu)建,兩或三個LSB可以使用二進制加權(quán)電流源。此類DAC在高頻時的失真非常低,這一點極其重要,而且設(shè)計中還有幾個重要問題需要考慮。

首先,電流不是接通或關(guān)閉,而是被導(dǎo)向一個地方或另一個地方。在高速運行時,關(guān)閉電流常常會引起感性尖峰,由于電容充電,它一般需要比電流導(dǎo)向更長的時間。

其次,芯片上開關(guān)電流所需的電壓變化應(yīng)盡可能小。電壓變化會導(dǎo)致更多電荷流入雜散電容,電荷耦合的毛刺也會更大。

最后,解碼必須在新數(shù)據(jù)應(yīng)用到DAC之前完成,使得所有數(shù)據(jù)均已就緒,可以同時應(yīng)用到DAC中的所有開關(guān)。其實現(xiàn)方式一般是對一個完全解碼陣列中的各個開關(guān)使用獨立的并聯(lián)鎖存器。如果所有開關(guān)瞬間同時改變狀態(tài),就不會有偏斜毛刺。只要精心設(shè)計芯片周圍的傳播延遲以及開關(guān)電阻和雜散電容的時間常數(shù),就能非常好地實現(xiàn)更新同步機制,因而毛刺相關(guān)的失真將非常小。

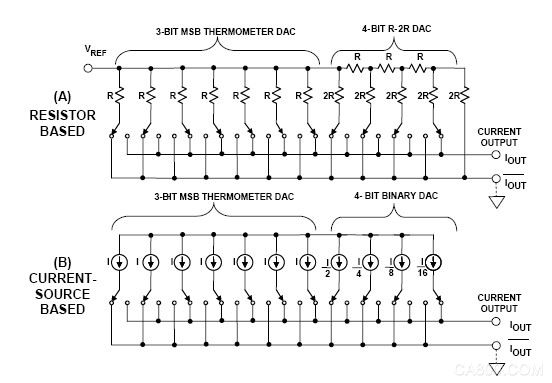

圖3顯示了分段電流輸出DAC結(jié)構(gòu)的兩個例子。圖3A所示為利用電阻方法實現(xiàn)7位DAC,其中3個MSB通過完全解碼獲得,4個LSB來自一個R-2R網(wǎng)絡(luò)。圖3B所示為使用電流源的類似實現(xiàn)方案。對于當今的高速重構(gòu)DAC,電流源方案是目前最受歡迎的實現(xiàn)方法。

圖3:分段電流輸出DAC:(A)電阻方案;(B)電流源方案

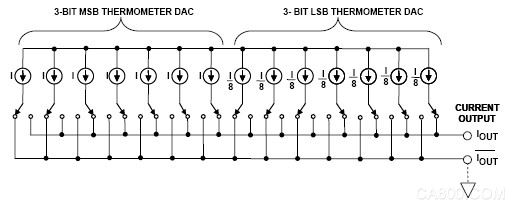

此外,常常也需要利用多個完全解碼DAC來構(gòu)成整個DAC。圖4所示的6位DAC由兩個完全解碼3位DAC構(gòu)成。如前所述,為使輸出毛刺最小,必須利用并聯(lián)鎖存器同時驅(qū)動這些電流開關(guān)。

圖4:基于兩個3位溫度計DAC的6位電流輸出分段DAC

AD977514位160 MSPS(輸入)/400 MSPS(輸出)TxDAC®使用三段,如圖5所示。AD977x系列的其它產(chǎn)品和AD985x系列也使用同樣的基本內(nèi)核。

圖5:AD9775 TxDAC®14位CMOS DAC內(nèi)核

前5位(MSB)為完全解碼型,驅(qū)動31個同等權(quán)重的電流開關(guān),各開關(guān)提供512 LSB的電流。后續(xù)4位解碼為15條線,驅(qū)動15個電流開關(guān),各開關(guān)提供32 LSB的電流。最后5個LSB位被鎖存,并驅(qū)動一個傳統(tǒng)二進制加權(quán)DAC,該DAC針對每個輸出電平提供1 LSB。為了實現(xiàn)這種超低毛刺架構(gòu),總共需要51個電流開關(guān)和鎖存器。

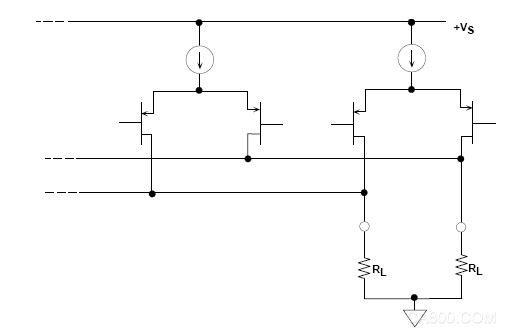

TxDAC系列中的基本電流開關(guān)單元由圖6所示的差分PMOS晶體管對組成。這些差分對通過低電平邏輯驅(qū)動,以便最大程度地降低開關(guān)瞬變和時間偏斜。DAC輸出為對稱的差分電流,有助于減少偶數(shù)階失真產(chǎn)物(特別是驅(qū)動變壓器或運放差分電流電壓轉(zhuǎn)換器等差分輸出時)。

AD977x TxDAC®系列和AD985x-DDS系列的總體架構(gòu)實現(xiàn)了功耗與性能的出色平衡,通過標準CMOS工藝就可以實現(xiàn)完整的DAC功能,無需薄膜電阻。

圖6:PMOS晶體管電流開關(guān)

參考文獻:

1.Dennis Dempsey and Christopher Gorman,"Digital-to-Analog Converter,"U.S.Patent 5,969,657,filed July 27,1997,issued October 19,1999.(描述一款出色的分段無緩沖串DAC解決方案)。

2.John A.Schoeff,"An Inherently Monotonic 12 Bit DAC,"IEEE Journal of Solid State Circuits,Vol.SC-14,No.6,December 1979,pp.904-911.(描述首個使用分段的一款單調(diào)DAC)。

3.Walt Kester,Analog-Digital Conversion,Analog Devices,2004,ISBN 0-916550-27-3,Chapter 3.另見The Data Conversion Handbook,Elsevier/Newnes,2005,ISBN 0-7506-7841-0,Chapter 3.